# Design and Performance Analysis of Over Current Relay under different Faults Scenarios

O.Thireesh<sup>1</sup>, N.Sudarsan Rao<sup>2</sup>, D.Jeevan Kumar Reddy<sup>3</sup>, D.Amulya<sup>4</sup>, CH.Malavika<sup>5</sup>, K.V.Dileep Kumar<sup>6</sup> <sup>1&2</sup>Assistant Professor, <sup>3,4,5&6</sup>UG Student

<sup>1,2,3,4,5&6</sup>Electrical & Electronics Engineering, Sree Venkateswara College of Engineering-Nellore, Andhra

This research work will develops an automatic tripping mechanism for the threephase supply system, following a fault in the transmission line. Whenever there Article Info is a fault, this proposed system will sense the fault and restricts the flow of supply Volume 8, Issue 3 to the grid-substations which are compressed of control gears without occurring Page Number : 274-281 more damage to them. For handling faults with long and short duration 555 timers are implemented. For the mechanism of tripping activation some switches are utilized to inject fault artificially. In the event of a temporary fault, the circuit will Publication Issue : automatically reset after a brief interruption, whereas in the event of a permanent May-June-2022 fault, the circuit will remain tripped. This primarily considers four cases: LLLG temporary fault, LLLG permanent fault, LLL temporary fault, and LLL permanent Article History fault. The main benefit of the project is that it saves the appliance, which prevents Accepted: 01 June 2022 damage to the load. The system only knows if there is a fault or not, and if the Published: 07 June 2022 fault is temporary, the supply is restored. If the fault is permanent, a permanent Pradesh, India trip signal is sent to the relay, and the supply to the load is restricted. Keywords : Overcurrent Relay, Grid, LLLG fault, LLL fault, 555 Times, Circuit ABSTRACT

Breaker

### I. INTRODUCTION

A fault in a power system is any abnormality in the electric current flowing through it. The following is an example of a fault occurrence. The open circuit fault occurs when the current is messed up due to the fault and the occurrence of short circuit due to current bypassing with normal load. In a three-phase system, the fault may occur between one or more phases and ground, or only between the system's phases. In general, protective devices are used in transmission systems to detect fault conditions and cause circuit breakers or isolators to operate, thereby limiting the damage caused by the failure. A fault in a three-phase or poly-phase system may affect some phases (resulting in asymmetrical operation). If all the phases are affected equally, it results in a symmetrical fault. Asymmetrical faults are more difficult to understand than symmetrical faults. To protect the power system transmission lines, faults must be accurately detected and isolated [1–2]. The control panel of a power system

42

Copyright: © the author(s), publisher and licensee Technoscience Academy. This is an open-access article distributed under the

terms of the Creative Commons Attribution Nondistribution, and reproduction in any medium, provided the original work is properly cited-Commercial License, which permits unrestricted non -commercial use,

contains numerous alarms that detect signals from various protection techniques for various types of fault. These flaws are either balanced or unbalanced. Electric power utility engineers have long been fascinated by the subject of fault location. Many electrical faults result in mechanical damage, which must be repaired before the line can be reconnected. If the location of the fault is known or can be estimated with reasonable accuracy, the restoration process can be sped up. The ability to detect, isolate, locate, and repair these faults quickly is critical for ensuring a reliable power system operation. The authors' goals in [3] are to clearly define each fault-locating algorithm's input data criteria, quantify the various sources of fault-locating error, demonstrate the application of each algorithm in locating real-world transmission line faults, and provide recommendations for selecting the best faultlocating approach. However, it only applies to distribution networks. The authors of [4] investigate the effect of different fault-locating error sources on a small number of algorithms [5] are excellent references for impedance-based fault location algorithms. Unfortunately, the discussion is limited to one-ended methods, and [6] does not cover all of the IEEE C37.114 impedance-based fault location algorithms. Some of the researchers proposed other methods for based on impedance measurements, phasor measurements, neural networks, and traveling waves. This methods use single terminal data and the others use double terminal data. The location of the fault point is simply estimated utilizing voltage and current measurements taken at line ends. Fault location can be estimated with varying degrees of accuracy using appropriate mathematical models and algorithms. In single terminal methods, an extra assumption must be added to the model. This assumption reduces the accuracy of these methods. Some parameters such as source impedance, pre-fault data, and sampling frequency have a major effect on different algorithms [8]-[9]. As proposed in [10] a novel approach, in which new type of magnetic sensors are deployed at the tower location, and the magnetic field signals are acquired and sent back to monitoring center. Then the fault location can

be found and the type of faults can be identified by analyzing the measured signals. This approach is advantageous over traditional approaches in that it is independent of the distributed line parameters and has a location error smaller than one span. The fast progress in magneto-resistance sensor technology can actually enable a lot of applications in transmission line monitoring applications [11]. As proposed in [12], [13] have proposed new accurate fault location method based on computing the voltage profiles along the line using two-end of the line. As we know, it is impossible to calculate the voltage profile using one terminal data for a faulted line. If we regard the faulted line as healthy line, we can get a voltage profile using singleended data, although the profile is not true behind the fault point, we call this profile as "fictitious voltage profile". As proposed in [14]-[15], some switches are implemented for injecting the faults. This paper proposes a novel terminology of reclosing mechanism in the supply line. Section-I describes about the introduction and literature of the existing methods, Section-II depicts about description of the system and Section-III explains about the protective proposed system, Section-IV explains about both experimental setup and simulation based results and the last section will depicts about the conclusion of this project compared to the conventional methods.

## II. DESCRIPTION OF THE SYSTEM

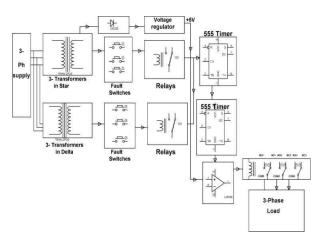

Figure 1: Experimental setup of the proposed system

The prototype model of the fault clearing system is shown in Figure 1. Six transformers known as step down transformers are primarily considered in this work for the analysis of faults in a three-phase system. The primary of three transformers is connected to a three-phase supply in a star configuration, and the secondary is also connected in a star configuration. The other set of three transformers has a three-phase primary connected in star and a delta secondary. Each of the six transformers' output is rectified and filtered separately before being routed to six relay coils. The six push buttons, one of which is connected across the relay coil, are designed to cause a fault condition at the star, such as LL Fault or 3 L Fault. All NC contacts on the relays are made parallel, and all common points are grounded. The parallel connected point of NC is fed to pin 2 of a 555 timer via a mono-stable resistor R5. Two 555ICs are used in the control circuit diagram of the fault clearing prototype, one in monostable mode and the other in isolated mode. The same timer's output is connected to the reset pin 4 of another mono-stable 5 5 5timer. LEDs are connected at their output to indicate their status. The U2 555 timer output from pin3 is connected to an Op-amp LM358 via wire 11 and dl2 to the non-inverting input pin3, while a potential divider RV2 keeps the inverting input at a constant voltage. The potential divider voltage at pin2 is held higher than the voltage at pin3 of the Op-amp used as a comparator, causing pinl to develop zero logic and fail to operate the relay via the driver transistor QI. This QI relay is a threecontact (3CO) relay, which means it is designed to disconnect the load in the event of a fault.

#### III. PROPOSED PROTECTIVE SYSTEM

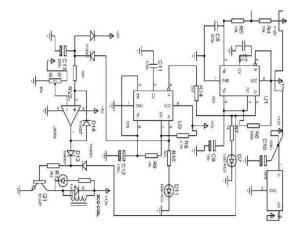

Figure 2 : Circuit Diagram of the proposed protective system

Whereas the panel is generated by a three-phase supply, all six relay coils receive DC voltage, and their common point disconnects from the NC and moves on to the NO points, providing logic high at pin2 of the mono-stable 555 timer U1. When any push button across the relay is pressed, it disconnects the relay and moves the common contacts to the NC position to provide a logic low at the 555 timer's trigger pin to develop an output that brings the U3 555 timer, which is used in a stable mode for its reset pin, to high such that the mono-stable operation takes place at its output, which is also indicated by flashing LED of D1.

If the fault is transitory, i.e. if the switch is activated and quickly released, the U1 mono-stable disables U3, causing its output to be zero. If the push button is held down for an extended period of time, the monostable output provides a longer duration active situation for U3, the astable timer, the output of which charges capacitor Cl 3 through R11, causing the comparator output to go high and the relay to turn off. Because of positive feedback provided by a forward reverse biased and a series resistor, the Opoutput amp's remains high indefinitely. As a result, the relay remains activated indefinitely to disconnect the load connected at its NC contacts. To keep the DC supply flowing, the starconnected secondary set DC's are paralleled through D8, D9, and D10 to provide an uninterrupted supply to the 12v DC and 5v DC circuit voltages derived from voltage regulator IC 7805.

#### IV. RESULTS AND DISCUSSION

The analysis of faults has been done through the simulation based results. The simulation results are evaluated by using Matlab/Simulink Software. Mainly two types of faults are considered namely Line-lineline-ground (LLLG) fault and line-line-line (LLL) fault. This fault types are majorily focused on current and voltage components. The occurrence of faults will be of cases permanent fault and temporary fault.

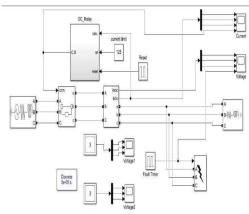

Figure 4 : Simulation diagram for fault analysis

The above figure-4 will depicts about the simulink model of the proposed system. In this the supply is taken from the 3-phase AC supply and a circuit breaker is connected make or break the circuit at the time of fault occurrence. An overcurrent relay is connected to the circuit breaker. A switch is connected for the creation of fault in the system. The obtained output is given to the load. Fault is injected in between the supply and load. The faults considered in this work, are of two types LLLG fault and LLL fault in two modes permanent mode and temporary mode with voltage and current components.

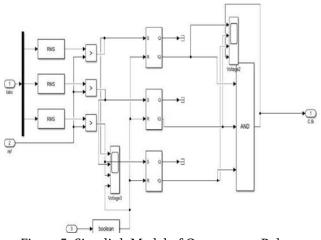

Figure 5: Simulink Model of Overcurrent Relay

The relay which is operating when the current exceeds the preset value is known as overcurrent relay. The simulink model of overcurrent relay is depicted in the above figure-5. In this work the instantaneous overcurrent is implemented. If the RMS currents is greater than the reference current then the circuit breaker will goes to trip position. So by this we can conclude that the fault has been occurred in the system. This related results of simulation are depicted below.

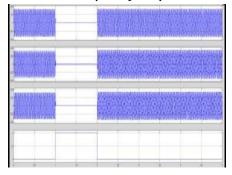

# A. Case-i: LLLG Temporary Fault:

In this case line-line-ground fault in temporary mode is considered and the obtained voltage and current related results are shown below. Momentary disruptions are caused by temporary faults.

# O. Thireesh et al Int. J. Sci. Res. Comput. Sci. Eng. Inf. Technol, May-June-2022, 8 (3): 42-52

Figure 6: Simulation based results of LLLG temporary faults occurred in Voltage and Current

Figure 7 : Simulation based results of LLLG

permanent faults occurred in Voltage and Current

From the above figures it can be depicted that the

waveform of voltage is in sinusoidal constant from 0s

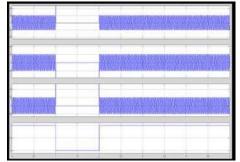

In this case-ii, the waveform of the voltage is in to 1s with amplitude of 320V and from 1s to 2s the sinusoidal from 0s to 1s with a value ranging from - amplitude is decreased to 0 due to occurrence of fault

320V to 320V, at 2s the amplitude of the waveform is

and goes to normal position once after the fault is decreased to zero and it continues the same till 5s cleared. In the similar manner the waveform of the with some distortions due to unavailability of current is in sinusoidal form with a value ranging protecting circuit or device. In the similar manner the from -20V to 20V and it is decreased to 0V due to waveform of the current is in sinusoidal form with a occurrence of fault and it comes to normal position value ranging from -20V to 20V and it is decreased to once after the fault is cleared. This is the temporary

0V due to occurrence of fault and it still continues LLLG fault. upto 5s due to unavailability of protecting device.

This is permanent LLLG fault.

Case-ii: LLLG Permanent Fault:

Permanent faults causes sustained disruption if not

cleared by protection. In this case Line-line-

Case-iii: LLL Temporary Fault: Case-iii: LLL Temporary Fault:

ground fault is in permanent mode. The obtained current and voltage waveforms are depicted below.

Figure 9: Simulation based results of LLL permanent Figure 8: Simulation based results of LLL temporary faults occurred in Voltage and Current faults occurred in voltage and current

In this case-ii, the waveform of the voltage is in

From the above figures it can be depicted that the sinusoidal from 0s to 1s with a value ranging from - waveform of voltage is in sinusoidal constant from 0s

320V to 320V, at 2s the amplitude of the waveform is

to 1s with amplitude of 320V and from 1s to 2s the decreased and varies from -200V to 200V and it amplitude is decreased to -200V to 200V due to continues the same till 5s with some distortions due occurrence of fault and goes to normal position once to unavailability of protecting circuit or device. In the after the fault is cleared. In the similar manner the similar manner the waveform of the current is in waveform of the current is in sinusoidal form with a sinusoidal form with a value ranging from -20V to value ranging from -20V to 20V and it is decreased to

20V and it is decreased to 0V due to occurrence of

0V due to occurrence of fault and it comes to normal fault and it still continues upto 5s due to position once after the fault is cleared. This is the unavailability of protecting device. This is permanent temporary LLLG fault occurred in voltage and

LLL fault.

currents.

V. CONCLUSION

Case-iv: LLL Permanent Fault

| Printed for Man |   |

|-----------------|---|

|                 |   |

|                 |   |

|                 |   |

|                 | _ |

of this proposed system is implemented by using Matlab/Simulink Software.

# VI. REFERENCES

- L. Heda, P. Bhutada, R. Thakur, P. Bhattad, and V. Singh, "Fault Monitoring and Protection of Three Phase Devices", International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering, Vol. 4, No. 4, April (2016).

- [2]. M. H. Idris, Member, IEEE, M. W. Mustafa, Member, IEEE and Y. Yatim, "Effective TwoTerminal Single Line to Ground Fault Location Algorithm", June 2012

- [3]. T. Kawady and J. Stenzel. "Investigation of practical problems for digital fault location algorithms based on EMTP simulation", AsiaPacific Transmission and Distribution Conference and Exhibition, 2002, Vol. 1, pp.118-123

- [4]. G. Ban, L.Prikier, "Fault Location on EHV Lines Based On Electromagnetic Transients", IEEE/NTUA Athens Power Tech Conference, 1993, pp. 936 – 940.

In this research work, design and performance analysis of overcurrent relay under different scenarios is implemented. Whenever there is a fault, this proposed system will sense the fault and restricts the flow of supply to the grid-substations which are compressed of control gears without occurring more damage to them. For handling faults with long and short duration 555 timers are implemented. For the

mechanism of tripping activation some switches are utilized

- to inject fault artificially. Mainly four cases are considered namely LLLG temporary fault, LLLG permanent fault and LLL temporary fault, LLL permanent fault. These faults are evaluated in voltage and current waveforms. For analyzing the faults 555 timer has been used with relay. The simulation results

- [5]. F. H. Magnago, A. Abur, "Fault location using wavelets," IEEE Transactions on Power Delivery, 13, 1998, 1475- 1480

- [6]. D. C. Robertson, O. I. Camps, J. S. Mayer, and W.

B. Gish, "Wavelets and Electromagnetic Power System Transients", IEEE Transactions on Power Delivery, Vol.11, No.2, pp. 10501058, April 1996.

- [7]. S. Sajedi, F. Khalifeh, Z. Khalifeh, T. karimi, "Application of Wavelet Transform for Identification of Fault Location on Transmission Lines," 2011.

- [8]. Lin, Y.H.; Lio,C.W.; Yu,C.S.; "A New Fault Locator for Three Terminal Transmission Line Using Two-Terminal Synchronized Voltage and Current Phasors", IEEE Trans. Power Del., vol. 17, no. 2, p.p. 452–459, Apr. 2002.

- [9]. Yu, C.S.; Liu,C.W.; Lin,Y.H; " A Fault location Algorithm For Transmission Lines with Tapped Leg-PMU Based Approach," in Proc. Power Eng. Soc. Summer Meeting, vol. 2, p.p. 915–920. Jul. 2001.

- [10]. Qi Huang, Wei Zhen, P.W.T. Pong. A Novel Approach for Fault Location of Overhead Transmission Line With Noncontact MagneticField Measurement. IEEE Transactions

on Power Delivery, Vol. 27 (3), 2012, pp. 1186 – 1195.

- [11]. X. Sun, K. S. Lui, K. K. Y. Wong, W. K. Lee, Y. Hou, Q. Huang, P. W. T. Pong. Novel Application of Magneto-resistive Sensors for High Voltage Transmission-Line Monitoring. IEEE Transactions on Magnetics, Vol. 47 (10), 2011, pp. 2608-2611.

- [12]. A. Gopalakrishnan, M. Kezunovic, S. M. McKenna, and D. M. Hamai, "Fault location using the distributed parameter transmission line model," IEEE Trans. Power Delivery, vol. 15, pp. 1169–1174, Oct. 2000.

- [13]. A. T. Johns and S. Jamali, "Accurate fault location technique for power transmission lines," Proc. Inst. Elect. Eng. C, vol. 137, no. 6, pp. 395–402, 1990.

- [14]. M.S. Morey, A. Ghodmare, V. Khomane, A. Singh, J. Dawande, and S. Ali Iqbal Shaikh, "Microcontroller Based Three Phase Fault Analysis for Temporary and Permanent Fault", International Research Journal of Engineering and Technology (IRJET), Vol. 02, No. 01, March (2015).

- [15]. M.S. Morey, A. Ghodmare, V. Khomane, A. Singh, J. Dawande, and S. Ali Iqbal Shaikh, "Microcontroller Based Three Phase Fault Analysis for Temporary and Permanent Fault", International Research Journal of Engineering and Technology (IRJET), Vol. 02, No. 01, March (2015).

# Authors profile:

Mr. O.THIREESH, received graduate degree in electrical and electronics engineering from JNTUH, HYDERABAD and post graduation degree specialisation of electrical power systems from JNTUK, KAKINADA and presently working as assistant professor in EEE Department At Sree Venkateswara College of Engineering, North Rajupalem, S.P.S.R Nellore, A.P. E- mail I'd: <u>triteesh.electrical@gmail.com</u>

MR. N SUDARSHAN RAO, received graduate degree in electrical and electronics engineering from JNTUA,

Anantapuramu and post graduation degree specialisation of electrical power systems from JNTUA, Anantapuramu and presently working as assistant professor in EEE Department At Sree Venkateswara College of Engineering,

North Rajupalem, S.P.S.R Nellore, A.P. E-mail I'd:- <u>n.sudarsanrao@svcn.ac.in</u>

D.JEEVAN KUMAR REDDY is Pursuing B.TECH in Electrical And Electronics Engineering from Sree Venkateswara College of Engineering, North Rajupalem, S.P.S.R Nellore, A.P. E-mail I'd:-

jeevanreddyjkr143@gmail.com

D.AMULYA is Pursuing B.TECH in Electrical And Electronics Engineering from Sree Venkateswara College of Engineering, North Rajupalem, S.P.S.R Nellore, A.P. E-mail I'd:amulyaduddu2001@gmail.com CH.MALAVIKA is Pursuing B.TECH in Electrical And

Electronics Engineering from Sree Venkateswara College of

Engineering, North Rajupalem, S.P.S.R Nellore, A.P. E-mail I'd:- <u>chavanamalavika@gmail.com</u>

K.DILEEP KUMAR is Pursuing B.TECH in Electrical And Electronics Engineering from Sree Venkateswara College of Engineering, North Rajupalem, S.P.S.R Nellore, A.P. E-mail I'd:-

kandalavenkatadileepkumar@gmail.com

Cite this article as :

O. Thireesh, N. Sudarsan Rao, D. Jeevan Kumar Reddy, D.Amulya, CH. Malavika, K. V. Dileep Kumar, "Design and Performance Analysis of Over Current Relay under different Faults Scenarios ", International Journal of Scientific Research in Computer Science, Engineering and Information Technology (IJSRCSEIT), ISSN : 2456-3307, Volume 8 Issue 3, pp. 274-281, May-June 2022. Journal URL : https://ijsrcseit.com/CSEIT228384